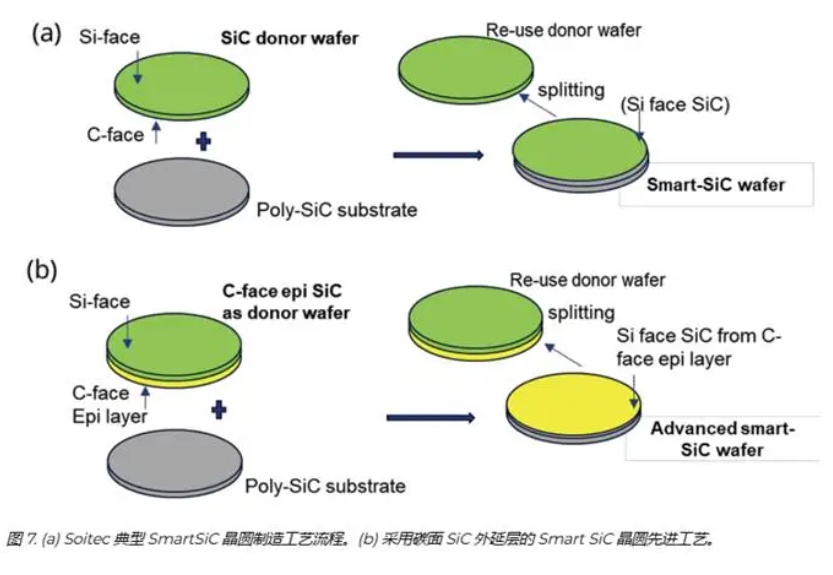

中国粉体网讯 近日,新加坡A-STAR微电子研究所和法国SOITEC发表了一篇文章,题为《SiC外延片迈向无缺陷》。

我们经常说的SiC外延,指的是SiC材料的衬底上生长一层具有特定晶体取向的SiC单晶薄膜的过程。其可以制造各类功率器件,可用于新能源汽车、光伏储能、航空航天等领域;氮化镓外延可以制造各类射频器件,用于5G通讯、雷达等领域。因此,SiC外延层的质量直接影响器件的性能和可靠性,而SiC外延工艺不可避免地会形成各种缺陷,影响SiC功率器件的性能与可靠性,缺陷控制也是SiC外延的一大难题。

文中披露,目前市售的6英寸和8英寸衬底已经可以做到无微管且位错密度较低:基面位错小于500个/cm2,穿刃位错和螺位错均低于5000个/cm2。但是为了制备高质量的碳化硅器件,仍需要优化碳化硅外延来进一步降低缺陷密度,尤其是“致命缺陷”。

目前,该团队实现了2个突破:

碳面SiC外延:在6英寸碳面SiC衬底上生产了几乎无缺陷的SiC外延,生长速率约为50微米/小时。该外延片表面光滑,均方根粗糙度略低于0.3nm,缺陷密度小于0.1个/cm2,5×5mm2器件的良率高达98.5%,为碳面SiC 器件带来了显著优势,尤其是在双极器件等大尺寸器件架构中。

硅面SiC外延:在硅面SiC衬底上生产了基面位错密度小于0.05个/cm2的SiC外延。在8英寸碳化硅衬底上,通过在器件漂移层生长之前,将衬底中的基面位错转化为缓冲层中的穿刃位错,采用衬底原位刻蚀技术,一批八片SiC衬底的基面位错几乎消除,密度小于0.05个/cm2,缺陷密度从典型的1.0个/cm2降至仅0.3-0.4个/cm2。

该研究突破了碳化硅外延缺陷控制的瓶颈,近无缺陷外延层可显著降低SiC MOSFET的导通电阻与开关损耗,提升双极器件(如IGBT兼容结构)的可靠性。50 微米/小时的高生长速率缩短外延时间,结合缺陷密度降低带来的良率提升,有望推动SiC功率器件成本下降。

那么,SiC外延常见的缺陷有哪些?又是怎么形成的?

外延层的缺陷种类非常多,形成机制也很复杂,总体上可以分成三大类:晶体缺陷、表面形貌缺陷以及扩展缺陷。

微管缺陷

微管缺陷是一个和螺型位错高度相关的空核芯,螺型位错的核芯周围的应变很高,通过化学键的断裂形成微观针孔。它是一个沿<0001>晶向扩展穿过整个SiC晶圆的针孔,直径范围从几分之一微米到几十微米不等,通常密度约为0.1~1 cm-2,在商业化晶圆生产中持续下降。

当SiC器件存在这样的一个微管时,注定会表现出高漏电和过早击穿的现象。要避免这种现象,就是将一个螺型位错从另一个螺型位错中分离出来,这样多次重复这个过程,一个微管缺陷就可以被彻底分解。

位错

目前4H-SiC同质外延层中的大多数位错都来源于衬底位错,衬底位错中又包括了贯穿螺型位错(TSD)、贯穿刃型位错(TED)和基面位错(BPD)。

螺位错(TSD):螺位错是由晶体中原子排列螺旋状偏离造成的。在碳化硅中,螺位错的Burgers矢量为<0001>,这意味着它们沿着晶体的c轴(生长轴)运行。螺位错在晶体生长过程中可能导致晶体结构的连续性受损,影响电子迁移率和器件的整体性能。

刃位错(TED):刃位错是由于晶体平面中原子排列的错位造成的。在碳化硅中,刃位错的Burgers矢量为1/3<11–20>,表明它们沿一个特定的晶面方向运行。这种类型的位错会导致晶体中局部应力集中,影响器件的电学特性,可能导致器件在高电流或高温下的不稳定性。

基面位错(BPDs)是碳化硅(SiC)晶体中一种重要的晶体缺陷,它们位于SiC晶体的基面上。BPDs在SiC晶圆表面不太常见,它们主要集中在衬底中,密度相对较高,通常在1500 cm-2的量级,而在外延层中的密度则大大降低,通常只有约10 cm-2。

堆垛层错(SF)是SiC基晶面中堆垛顺序混乱的缺陷。它们可能通过继承衬底中的SF出现在外延层,或与基晶面位错和螺位错的扩展和转化有关。

胡萝卜缺陷(Carrot Defect)是一种堆垛层错复合体,两端位于TSD和SF基晶面处,以Frank型位错终止。形成胡萝卜形状,密度小于1 cm-2。

三角形缺陷(Triangular Defect)可能由外延生长过程中SiC外延层表面的下坠颗粒产生。颗粒嵌入外延层并干扰生长,产生锐角三角形表面特征。

划痕(Scratches)是SiC晶圆表面的机械损伤,可能在外延层内产生高密度位错或成为胡萝卜缺陷形成的基础。抛光过程中的划痕会严重影响器件性能。

在SiC的外延生长过程中,螺位错(TSD)和刃位错(TED)是两种主要的位错类型,它们从衬底延伸到晶圆表面,并可能导致一些特定的表面特征和缺陷。这些位错在晶圆表面常表现为小的凹坑状特征。在外延生长过程中,扩展的螺位错不仅可以延伸到外延层,而且可能转化为其他类型的缺陷。这些螺位错沿生长轴传播,并有可能被转化为堆垛层错(SF)或胡萝卜缺陷。

来源:

半导体信息:推荐|碳化硅外延层缺陷简介

行家说三代半、清软微视

(中国粉体网编辑整理/空青)

注:图片非商业用途,存在侵权告知删除