中国粉体网讯 如果IBM Research的碳纳米管晶体管研究能有所突破,国际半导体技术蓝图(ITRS)的2028年硅材料“末日预言”时间将得以延续。根据IBM表示,研究人员们已经找到一种可将通道长度缩短至1.8nm节点(4个技术世代后)的方式,预计最终还将超越埃(angstrom;纳米的十分之一)等级。果真如此,摩尔定律(Moore's Law)就能沿用相同极紫外光(EUV)微影互补金属氧化物半导体(CMOS)工艺技术,顺利地延续到次纳米级(埃)工艺。

“1.2nm宽的碳纳米管通道已经证实可行了,”IBM华生研究中心(T.J. Watson Research Center)纳米科学与技术经理汉述仁表示,“微缩的主要问题不只出在碳纳米管,硅与III-V族材料(铟、镓、砷)的触点也存在无法微缩的挑战。”

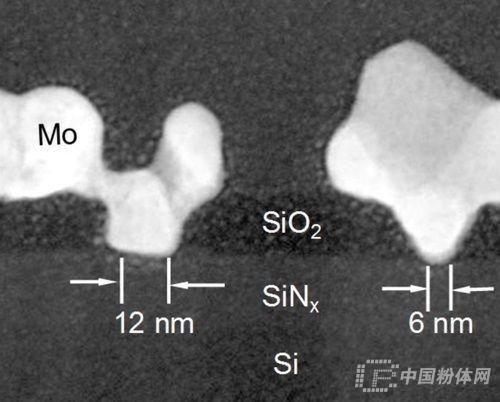

“我们已在最近取得了突破,”汉述仁指出,“如今了解了如何进行微缩,使其不再成为碳纳米管晶体管的限制因素。我们制作出新的触点,可测量至埃级,而且两端只有36kΩ。”

在经过长久的等待后,根据Envisioneering研究总监Richard Doherty表示,这项突破性的技术可望在不久后实现。

“毕竟,如果你还记得从贝尔实验室(Bell Labs)开发出触点晶体管到Fairchild和英特尔(Intel)连手打造出平面晶体管得花10年之久,就不会对于IBM得用另一个十年取得如此突破而感到意外了,”Doherty强调。

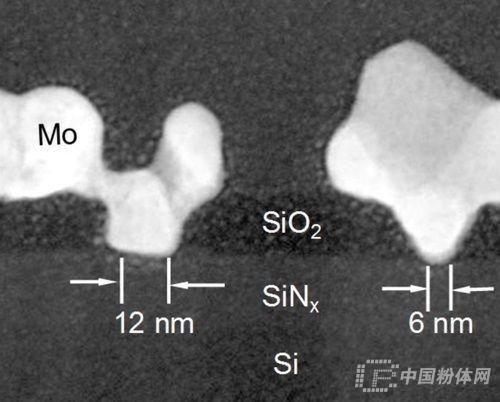

IBM经验证可用的芯片拥有9nm信道,但在取得这项突破以前,触点相形之下十分巨大。如今,IBM找到了一种能制作出较小触点的方法,能让它们微缩通道长度至1.8nm节点(约4个技术世代),最终还将超越埃等级。每一个节点只携带大约15mA,但IBM计划仅为设计中的特定位置同时使用许多碳纳米通道,从而解决这些问题。

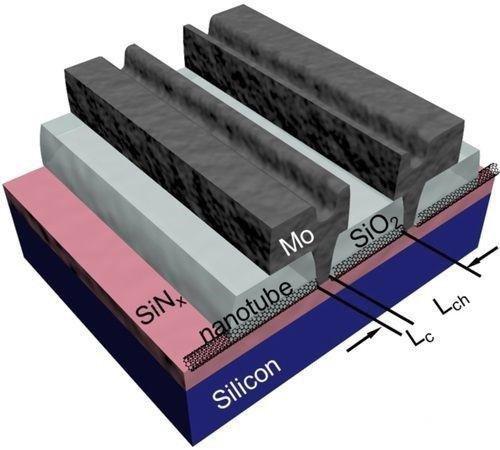

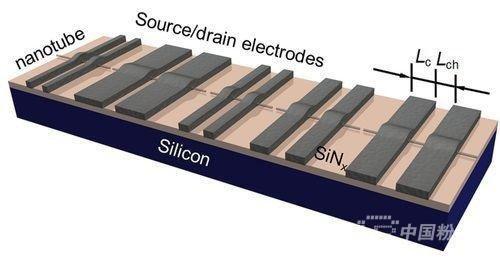

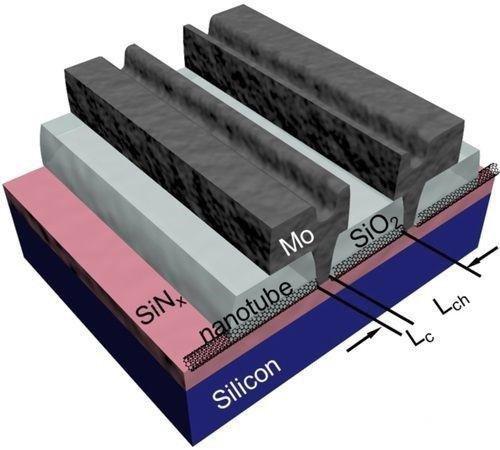

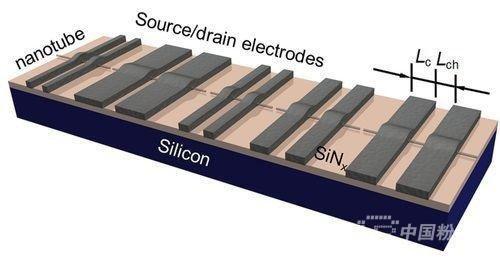

“利用自对准技术,我们能以8-10nm间距平行放置碳纳米管,”汉述仁透露,“我们用物理气相沈积(PVD)工艺为其进行沉积,然后再用高温退火——类似于显微焊接的冶金过程——以确保两端的通道触点稳定。”

Doherty对于IBM的“焊接”技术印象深刻,认为这将为IBM带来竞争优势。其方式是在碳纳米管自对准于晶体管通道以前,以钼涂布碳纳米管两端。然后加热整个组装至华氐1,562度(850℃而完成“焊接”过程,从而熔融钼并转化成为碳化物——一种可制作出优质埃级触点的导体。

开关电流切换率达10,000

“这项焊接/碳化物的新发现似乎是唯一有利于金属的硅工艺,而且不会产生氧化的问题,或是萧特基阻障层特性带来不必要的步进电压阈值。而IBM的方法可实现10,000的开关电流切换率,”Doherty指出,“其他尝试连接至纳米管的方式可能随时间进展而产生各种不同的电阻与导电特性,使其只能停留在实验室阶段。IBM的这项成果为实现真正的碳纳米管结构铺路,使其能够利用经验证可行的硅微影技术。”

IBM目前只能用其革命性“焊接”技术生产p型晶体管,但声称这些组件可运作得比FinFET更好。据汉述仁透露,该公司的下一步是在隧道终端使用光源,打造出n型组件,让CMOS碳纳米管晶体管可在3nm节点时进行制造,届时硅FinFET将达到5nm节点。

“IBM的内部目标是在5nm节点时准备就绪,并成为3nm节点一直到埃级以后的最佳选择,”汉述仁表示。

据Doherty表示,IBM的成果为延续摩尔定律带来了新希望,因为对于“焊接”技术来说,目前还没有什么不可突破的微缩问题。Doherty并将IBM的这项“焊接”技术称为“同轴连接”(coaxial connection)技术。

“随着摩尔定律的持续推向极限,硅晶变得越来越低效,而9nm通道的碳纳米管技术为业界带来了勇气和信心,让他们知道还有可替代的半导体路径存在,”Doherty强调,“同时,我也很少看到IBM的科学论文中有这么多研究人员共同带来了贡献。他们的目标是在十年内付诸生产,但我相信他们一定想尽可能更快达成。”

IBM的这项成果是其后硅晶技术计划的一部份,这项30亿美元的研发计划从2014年开始,目标在于为IBM所谓即将来临的“认知运算时代”所需要的运算需求而铺路。

“1.2nm宽的碳纳米管通道已经证实可行了,”IBM华生研究中心(T.J. Watson Research Center)纳米科学与技术经理汉述仁表示,“微缩的主要问题不只出在碳纳米管,硅与III-V族材料(铟、镓、砷)的触点也存在无法微缩的挑战。”

“我们已在最近取得了突破,”汉述仁指出,“如今了解了如何进行微缩,使其不再成为碳纳米管晶体管的限制因素。我们制作出新的触点,可测量至埃级,而且两端只有36kΩ。”

在经过长久的等待后,根据Envisioneering研究总监Richard Doherty表示,这项突破性的技术可望在不久后实现。

“毕竟,如果你还记得从贝尔实验室(Bell Labs)开发出触点晶体管到Fairchild和英特尔(Intel)连手打造出平面晶体管得花10年之久,就不会对于IBM得用另一个十年取得如此突破而感到意外了,”Doherty强调。

IBM经验证可用的芯片拥有9nm信道,但在取得这项突破以前,触点相形之下十分巨大。如今,IBM找到了一种能制作出较小触点的方法,能让它们微缩通道长度至1.8nm节点(约4个技术世代),最终还将超越埃等级。每一个节点只携带大约15mA,但IBM计划仅为设计中的特定位置同时使用许多碳纳米通道,从而解决这些问题。

“利用自对准技术,我们能以8-10nm间距平行放置碳纳米管,”汉述仁透露,“我们用物理气相沈积(PVD)工艺为其进行沉积,然后再用高温退火——类似于显微焊接的冶金过程——以确保两端的通道触点稳定。”

Doherty对于IBM的“焊接”技术印象深刻,认为这将为IBM带来竞争优势。其方式是在碳纳米管自对准于晶体管通道以前,以钼涂布碳纳米管两端。然后加热整个组装至华氐1,562度(850℃而完成“焊接”过程,从而熔融钼并转化成为碳化物——一种可制作出优质埃级触点的导体。

开关电流切换率达10,000

“这项焊接/碳化物的新发现似乎是唯一有利于金属的硅工艺,而且不会产生氧化的问题,或是萧特基阻障层特性带来不必要的步进电压阈值。而IBM的方法可实现10,000的开关电流切换率,”Doherty指出,“其他尝试连接至纳米管的方式可能随时间进展而产生各种不同的电阻与导电特性,使其只能停留在实验室阶段。IBM的这项成果为实现真正的碳纳米管结构铺路,使其能够利用经验证可行的硅微影技术。”

IBM目前只能用其革命性“焊接”技术生产p型晶体管,但声称这些组件可运作得比FinFET更好。据汉述仁透露,该公司的下一步是在隧道终端使用光源,打造出n型组件,让CMOS碳纳米管晶体管可在3nm节点时进行制造,届时硅FinFET将达到5nm节点。

“IBM的内部目标是在5nm节点时准备就绪,并成为3nm节点一直到埃级以后的最佳选择,”汉述仁表示。

据Doherty表示,IBM的成果为延续摩尔定律带来了新希望,因为对于“焊接”技术来说,目前还没有什么不可突破的微缩问题。Doherty并将IBM的这项“焊接”技术称为“同轴连接”(coaxial connection)技术。

“随着摩尔定律的持续推向极限,硅晶变得越来越低效,而9nm通道的碳纳米管技术为业界带来了勇气和信心,让他们知道还有可替代的半导体路径存在,”Doherty强调,“同时,我也很少看到IBM的科学论文中有这么多研究人员共同带来了贡献。他们的目标是在十年内付诸生产,但我相信他们一定想尽可能更快达成。”

IBM的这项成果是其后硅晶技术计划的一部份,这项30亿美元的研发计划从2014年开始,目标在于为IBM所谓即将来临的“认知运算时代”所需要的运算需求而铺路。