中国粉体网讯 随着电子设备向小型、多功能、大功率及高可靠性方向的快速发展,微电子器件高密度的三维集成技术应运而生。然而,高密度集成的发展受限于芯片热集中引起的高结温问题,严重导致器件性能和可靠性的下降。

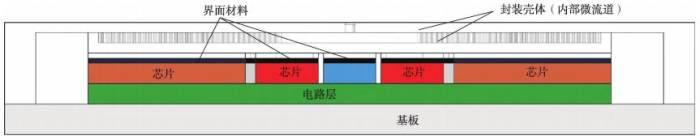

集成芯片内部为多层结构组合而成,依次为基板层、芯片电路层、芯片、封装壳体冷板。封装壳体冷板内部设计有微通道,通过液体对流换热带走电路层芯片的热量,并保证芯片均温性。封装壳体冷板与电路层之间采用柔性导热界面材料(TIM)过渡连接。

集成芯片散热示意图

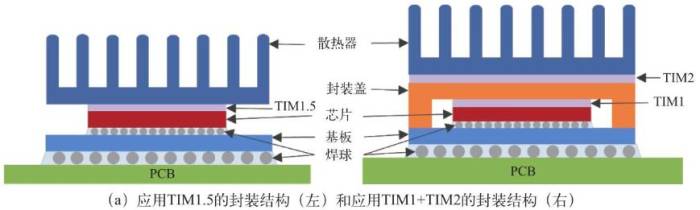

导热界面材料是一类重要的散热材料,它们用于填充两个表面之间的微小空隙,直接改善散热性能。TIM通常应用于芯片与封装盖(TIM1)、芯片与散热器(TIM1.5)、封装盖与散热器之间(TIM2)。高导热性、高可靠性的TIM能够保障热量在界面的快速传递。目前高算力芯片主流的散热方案还是通过超低热阻的TIM1材料将芯片内部的热量快速传导到封装外壳上,然后再通过TIM2材料将热量再次传导至液冷板上,液冷板通过内部冷却工质的快速流动将热量快速的传递到外部环境。

微流道散热技术是AI算力芯片封装较有技术前景的方案,微流道散热通过微米级通道将冷却液直接引入芯片核心区域,利用高比表面积实现高效热交换。微流道散热技术的核心在于将散热器从封装或模块外部移向内部,以减少结区至环境的热阻。与传统散热技术相比,微流道散热通过在芯片背部基底刻蚀和集成微通道,将冷却液直接输送至芯片结区热点附近,从而根本性地缩短热传导路径。其技术演进已实现三大突破:

(1)结构创新:从传统直通道到3D打印“淋浴喷头式”多孔结构,传热系数提升至10 W/m2·K;

(2)集成突破:与TSV三维集成技术融合,将冷却通道嵌入芯片转接板,热阻低至0.02℃·cm2/W;

(3)智能调控:结合AI算法动态分配流量,精准应对芯片“热点”,温度可降低50℃以上。

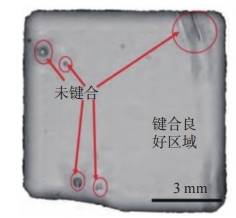

另外,在封装工艺中,低温键合技术得到了广泛应用。例如低温Cu-Cu键合技术因其在高密度互连、良好的导电性和导热性方面的优势,成为先进封装的核心技术之一。纳米银烧结工艺是低温键合技术的典型代表,可在250℃的低温条件下形成250 W/(m·K)高热导率的连接界面,有效避免了传统高温工艺带来的热致损伤。该工艺获得的连接结构孔隙率极低、热传导特性优异、机械稳定性突出,为先进封装提供了可靠保障。

Cu-Cu键合样品

2026年1月28日,中国粉体网将在广东•东莞举办“第三届高导热材料与应用技术大会暨导热填料技术研讨会”。届时,我们邀请到厦门大学马盛林教授出席本次大会并作题为《高算力AI芯片封装集成散热关键技术进展》的报告。报告将简要综述国内外高算力AI芯片集成散热技术研究进展,重点介绍团队在低温铜-铜键合、铟基TIM等关键材料与工艺的进展,在此基础上介绍FC封装芯片衬底集成微流道、多晶金刚石热沉片、直接喷射微流体散热等系列产品的研制进展。

专家简介

马盛林,厦门大学教授、博士生导师,主要从事集成电路先进封装(TSV/TGV,2.5D/3D)与热管理、PMUT等方向研究工作。近年来,主持国家自然科学基金重大研究计划项目、国家重点研发计划项目、厦门市科技重大专项课题等10余项,承担华为海思、中兴微电子等产学研项目30余项,以第一作者/通讯作者发表学术论文70余篇,出版学术专著3部,获授权专利、软件著作权等40余项,获省部级科学技术进步一等奖2项。

参考来源:

吴作栋等:三维集成芯片散热技术研究

马盛林等:面向先进封装应用的混合键合技术研究进展

(中国粉体网编辑整理/石语)

注:图片非商业用途,存在侵权请告知删除!