存储芯片集成密度的提升对于大容量存储和并行计算至关重要,这要求三维叠层交叉点架构中的选择器组件具备极低的漏电流和适当的阈值电压。目前三维相变存储器主要利用双向阈值开关选择器控制存储单元的通断,其访问性能直接影响芯片的面积效率和成本。理想的选择器应在半偏置电压下实现皮安级的亚阈值漏电流,并展现出极高的开关非线性度,同时阈值电压需维持在1.8至2.5伏特之间,以兼容先进工艺节点的低压逻辑器件。然而现有的材料体系和结构设计往往难以同时满足这些严苛的参数要求,制约了更大规模存储阵列的发展。

挑战在于传统选择器面临物理属性冲突的困境,通过增加材料交联度或插入介质缓冲层虽能降低漏电流,但往往会导致阈值电压不可避免地大幅升高。近期虽有通过降低传导激活能来压低电压的尝试,但其漏电流仍普遍高于纳安级别,且开关比受限。此外为了承受集成电路后端制备过程中的热预算,非晶态材料必须具备极高的热稳定性,但这通常会拉大电子带隙并提升开启门槛,另一个核心难题是选择器的丝状导电物理机制长期存在争议,且缺乏直接的实空间观测证据。

针对上述问题,由深圳大学、浙江大学等组成的团队利用泽攸科技的原位TEM测量系统进行了系统研究,通过设计一种具有卓越热稳定性的Ge?Se?非晶纳米粒子组装纳米层,利用其极小的电极接触面积显著抑制了选择器的亚阈值漏电流,并在国际上首次通过原位电子全息技术直接证实了纳米尺度的丝状导电机制。

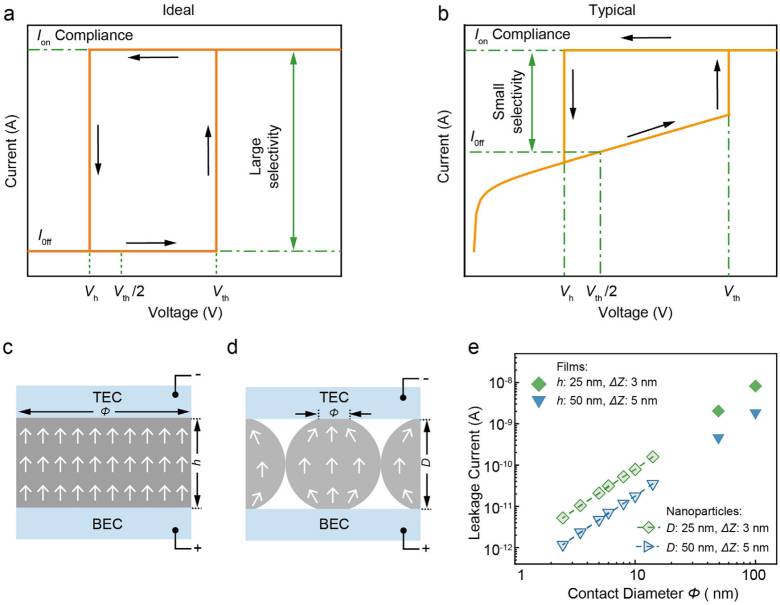

研究团队开发出一种全新的热注射合成技术,成功制备出Ge?Se?非晶球形纳米粒子,填补了该材料体系在纳米颗粒形态上的研究空白。这种材料在设计上追求简化二元组分且不含砷元素,有效降低了大规模生产的技术门槛。实验结果表明,该纳米粒子在氩气环境下即便加热至550摄氏度仍能保持非晶态,其结晶温度显著高于大多数现有的阈值开关薄膜材料。这种卓越的热稳定性使其能够完美兼容半导体制造中的后端工艺热预算,为高性能嵌入式存储器的应用奠定了坚实的物质基础。

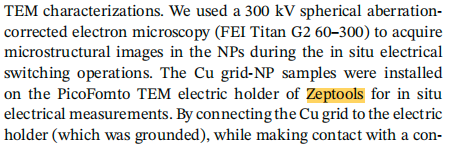

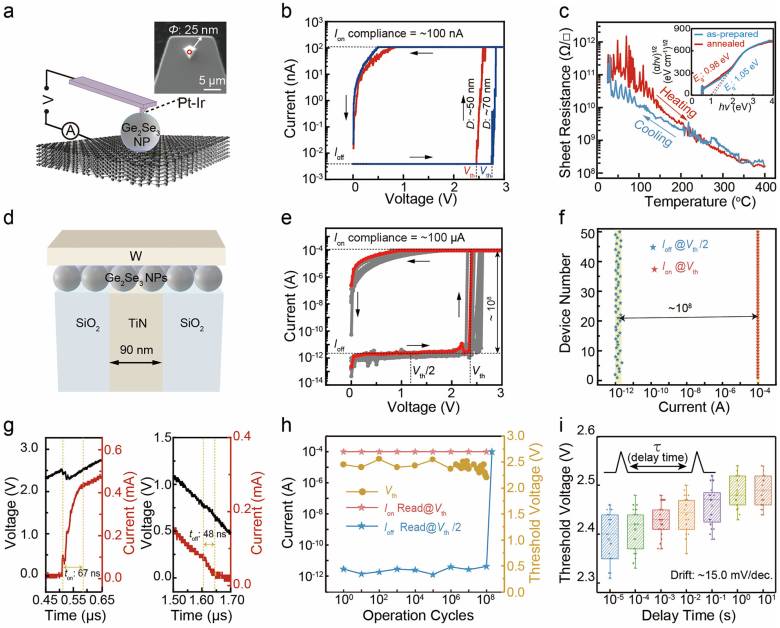

图1 纳米粒子组装纳米层OTS选择器的方案提出

图2 热稳定非晶态Ge?Se?纳米粒子的合成

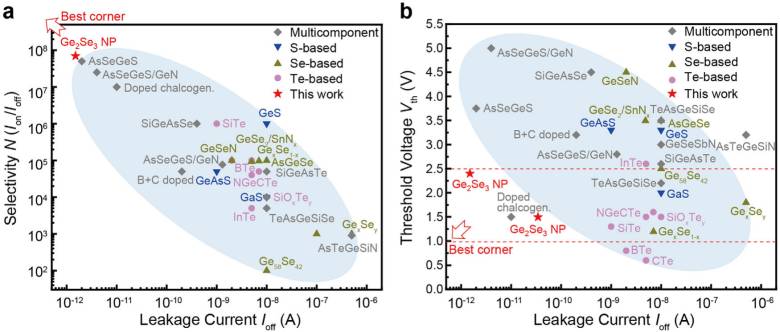

通过将这种非晶纳米粒子旋转涂布在衬底上,研究人员构建了一种宏观致密的纳米组装层,并将其集成至T型选择器器件中。得益于纳米粒子与电极之间极小的有效接触面积,该器件在保持阈值电压位于2.2至2.6伏特合理区间的同时,实现了约1皮安的极低亚阈值漏电流。这一成果直接带来了高达十的八次方的开关选择比,在关键性能指标上全面超越了现有的基于薄膜结构的同类选择器,这种通过物理形貌创新来解决电学性能冲突的设计思路,为三维交叉点架构的进一步微缩提供了可行路径。

图3 纳米粒子及纳米粒子组装纳米层选择器的访问性能

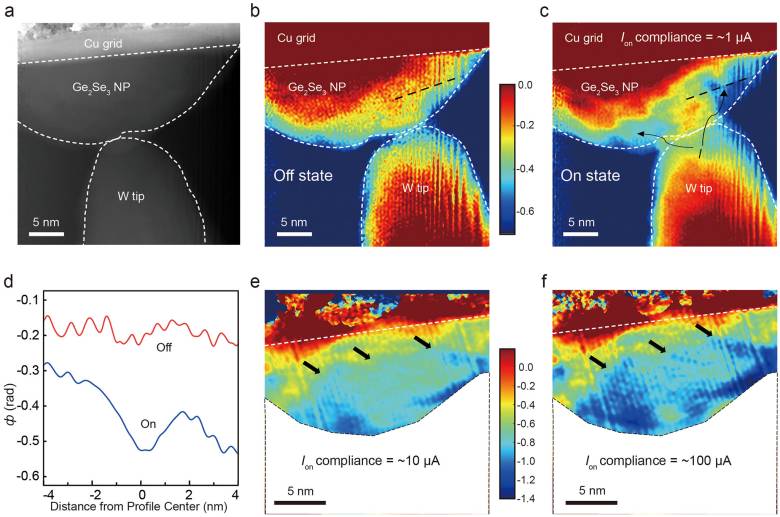

为了深入探究开关过程中的物理机制,研究团队利用泽攸科技提供的透射电镜原位样品杆对单个纳米粒子在电压驱动下的结构与电场变化进行了实时观测。通过该原位样品杆,科研人员能够在施加电压偏置的同时,利用球差校正电镜捕获高分辨率的微观图像。这种精密仪器的应用使得研究者能够精准控制电流合规值,从而在保持非晶状态的前提下观察粒子内部的导电演变。实验过程严格遵循了低电子束剂量原则,最大限度地减少了束流效应对样品潜在的损伤,确保了观测结果的真实性与高信度。

图4 与多种OTS材料的Ioff–N与Ioff–Vth性能对比

借助原位离轴电子全息技术,研究团队在国际上首次直接观测到了单个纳米粒子内部形成的纳米级导电丝状路径。在器件开启状态下,电子全息图清晰地显示出从微小接触点向外延伸的低电位感知区域,这与关闭状态下的全域高电位分布形成了鲜明对比。研究证实,随着驱动电流的增加,这些导电路径会经历从边缘生根到逐渐向内部扩张的过程,最终形成支撑高电流传输的有效通道。这一发现不仅为长期争论不休的阈值开关物理起源提供了关键性的实验支撑,也为未来开发超小尺寸的相变存储单元提供了重要的理论依据。

图5 用于证实丝状导电的原位离轴电子全息技术

泽攸科技作为中国本土的高端精密仪器公司,是原位电子显微镜表征解决方案的一流供应商,推出的PicoFemto系列的原位透射电子显微镜表征解决方案,陆续为国内外用户的重磅研究成果提供了技术支持。下图为该研究成果中用到的泽攸科技原位TEM样品杆产品:

FEI双倾探针杆